A Methodology for NoC

AST Grenoble Marcello Coppola

# Outline

- Toolip overview

- SoC today

- NoC

- OCCN

- Test study

- Conclusion

# **TOOLIP** Focus

- Residential and home applications are becoming increasingly complex systems and application

- Industry requires a high level of integration of various functions

- Integration of whole systems on a single chip

#### Manage complexity by

- Parametric and reusable IP cores

- System-level modelling

- Verification techniques

- Design flow

- IP Qualification

#### **Objectives:**

- Shorten design times cycles

- First time silicon success

- Reducing design complexity

- Ease simulation, verification and test

- Make "reuse" a feasible reality

#### **TOOLIP** Partners

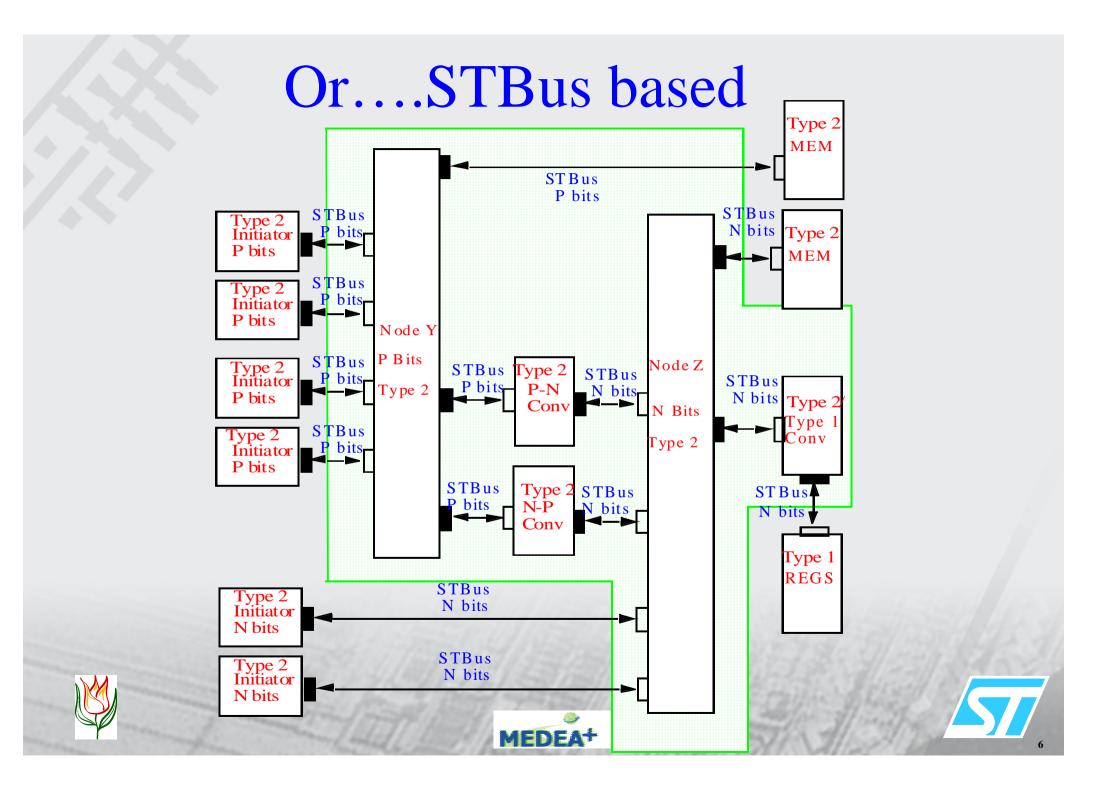

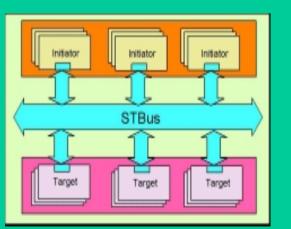

### **STBus Interfaces**

| Interface Type                                                                                                                                          | <u>Initiator</u>                      | <u>Target</u>                                    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|--------------------------------------------------|

| <b>Type 1 : Peripheral</b> - Simple synchronous handshake - Limited transaction set                                                                     | ST20-C1                               | Peripherals (UART,<br>timer)<br>On-chip SRAM ROM |

| <b>Type 2 : Basic System</b> - Supports split, pipelined accesses                                                                                       | ST20-C2 core<br>customer ASICs        | Flash EMI<br>SDRAM EMI                           |

| <b>Type 3 : Advanced System</b> <ul> <li>Supports split, pipelined accesses</li> <li>Supports out of order execution</li> <li>Shaped packets</li> </ul> | ST40 / ST50 Core<br>multi-channel dma | PCI master<br>DDR LMI                            |

# **STBus Building Blocks**

□Node

Performing arbitration and routing

Buffer

Performing retiming

Size Converter

Allowing the communication between two blocks having different bus sizes

#### Type Converter

Allowing the communication between two blocks following different STBus protocols

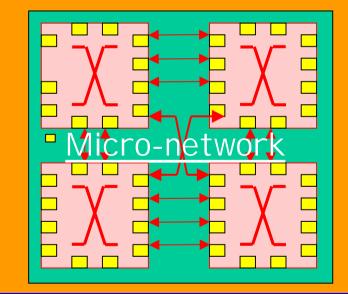

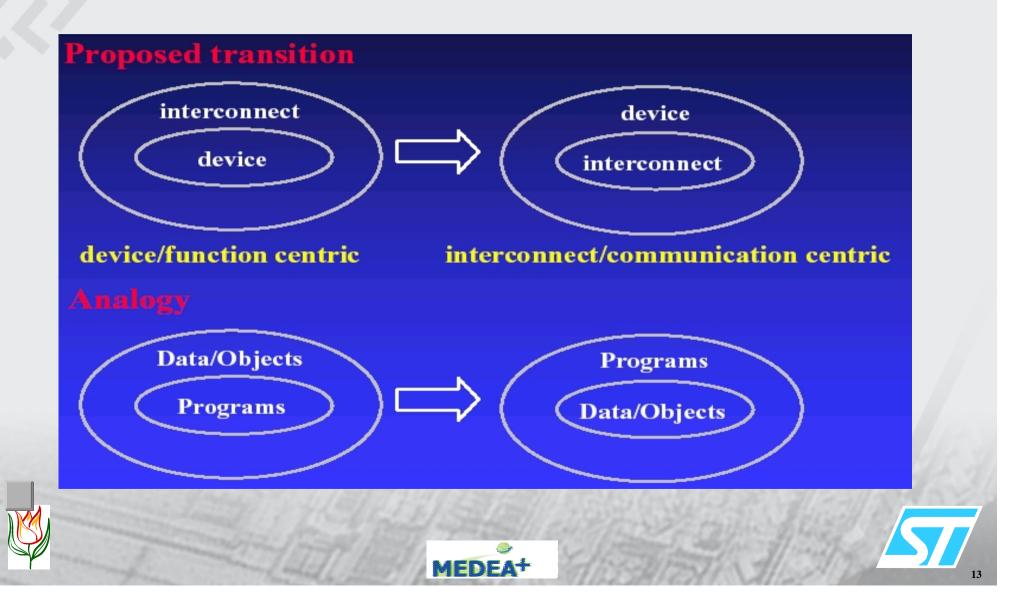

## From SoC to NoC

#### System on a chip

Programmable computation Hardwired interconnectivity Partially distributed storage

#### Network on a chip

Programmable computation Programmable interconnectivity Fully distributed storage

### Some definitions

- NoC is a future view as a micro-network of components [Benini and De-Micheli]

- NoC is a parallel computation platform with a task/process level of parallelism; suitable only for high-volume products [J.P Soininen and H Heusala]

- NoC is a set of computation node connected via sophisticated on-chip communication network [A.A Jerraya et alt.]

#### **Communication Centric Methodology**

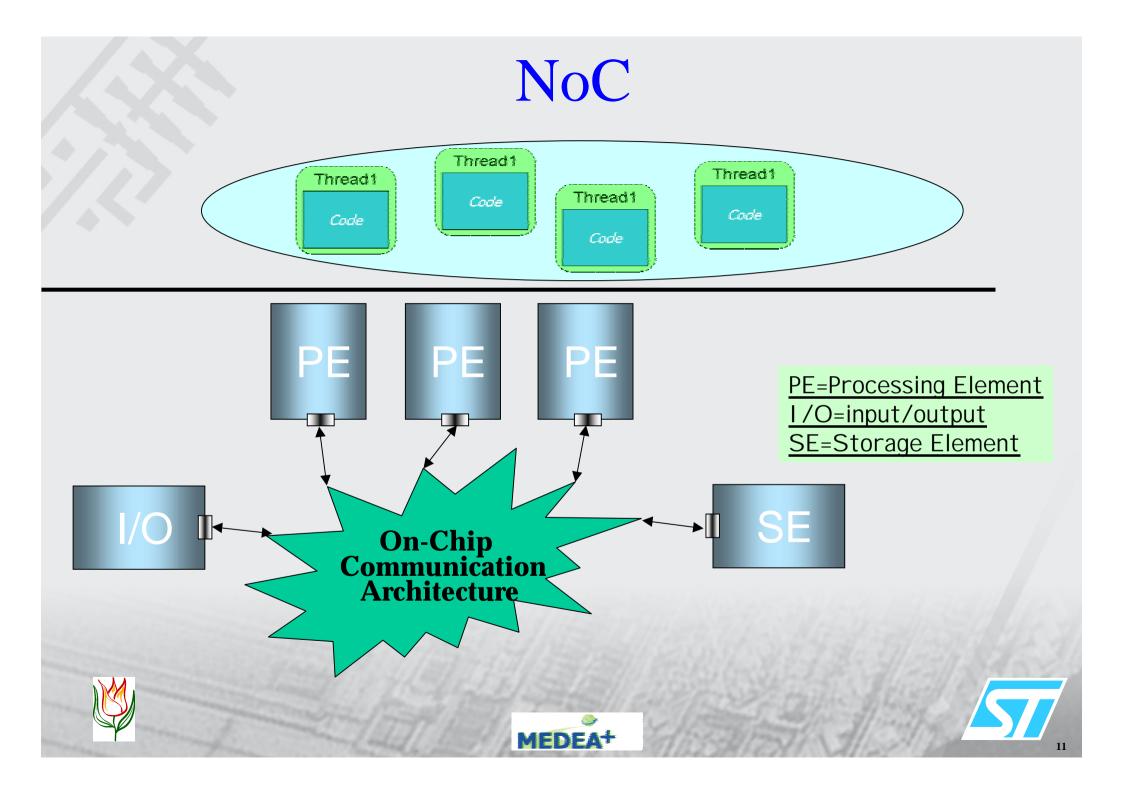

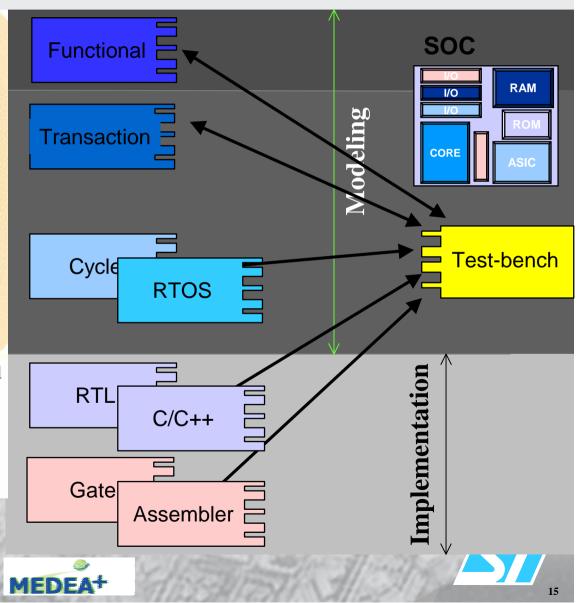

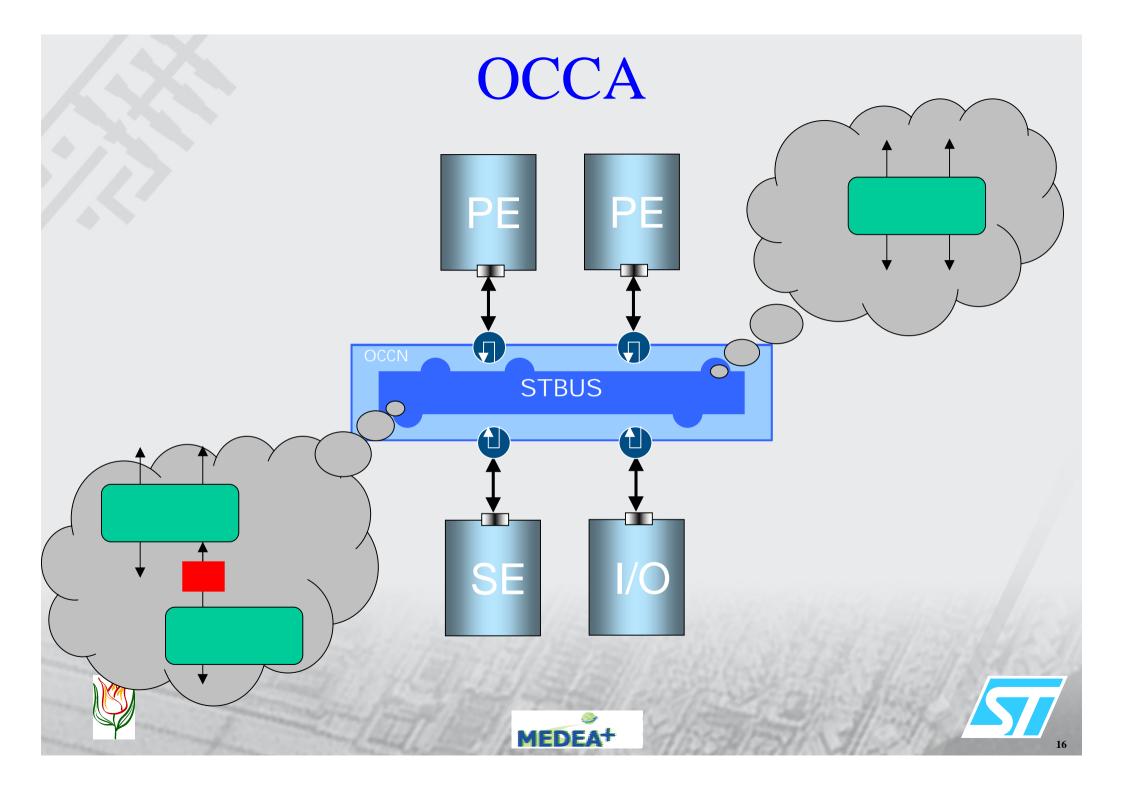

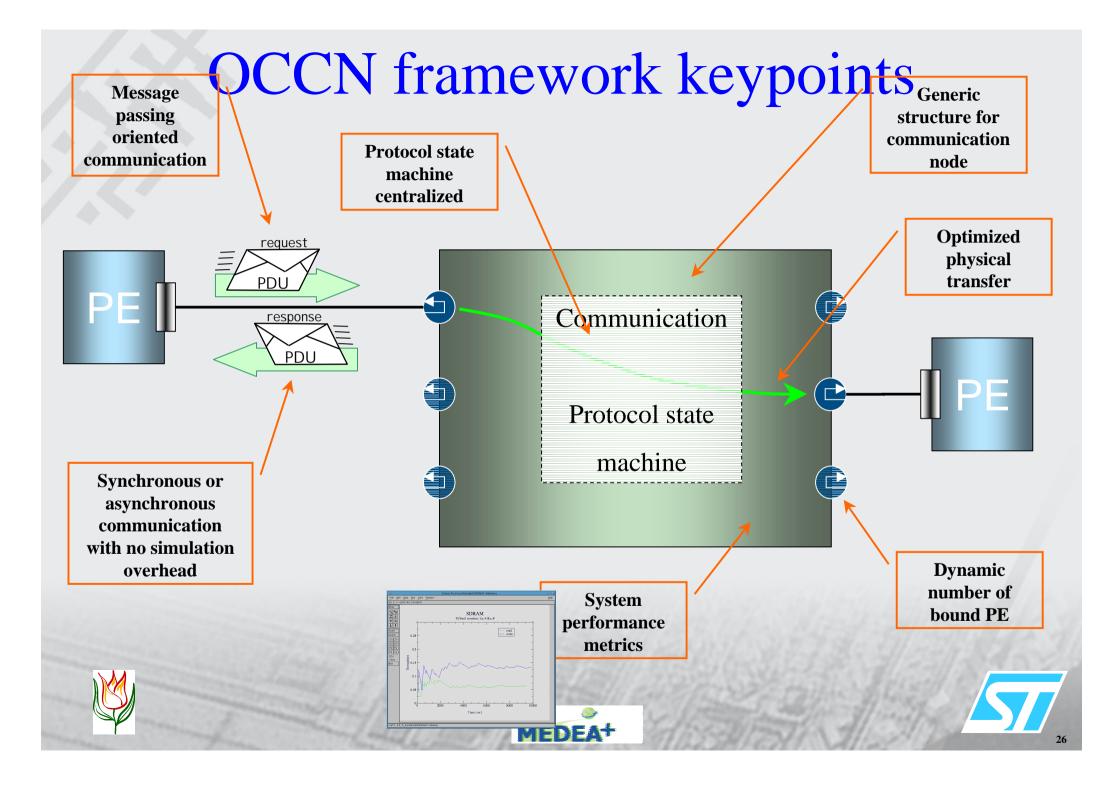

# OCCN : methodology for

- Communication modeling

Generic communication-centric design methodology based on C++ and SystemC

- OCCN addresses

- high level performance modeling issues such speed, latency and power estimation

- modeling productivity

- model portability

- simulation speed-up

- OCCN is an on-going research activity between several R&D organizations

**On-Chip**

communication

architecture

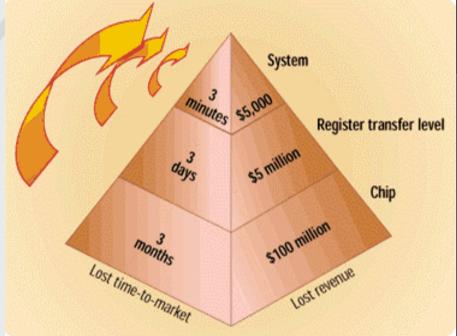

#### **Compromise: Multi-levels Validation**

Source: Integrated Communications Design May, 2001

Higher Abstraction layer implies shorter Iteration Cycles and less Lost Revenue

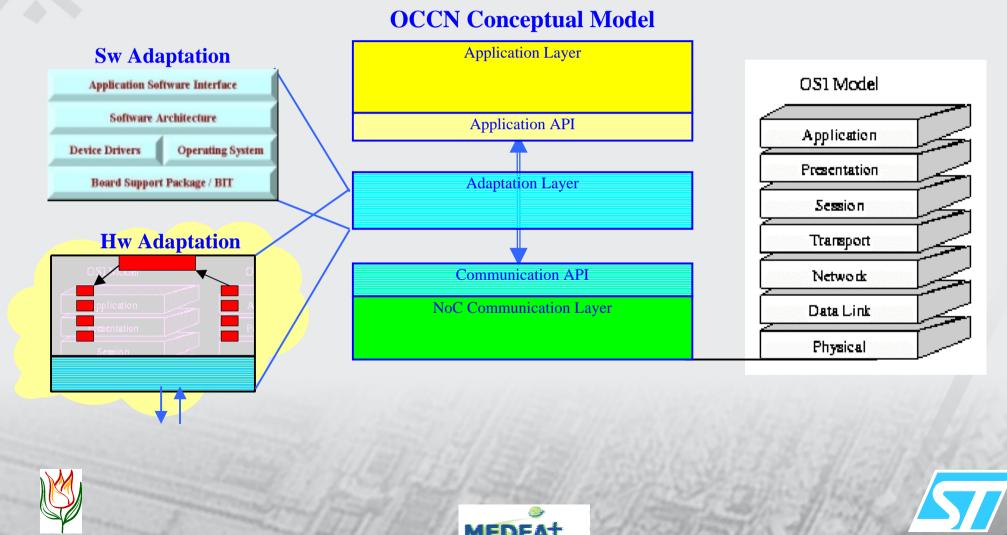

# **OCCN** Conceptual Model

17

#### What is OCCN ?

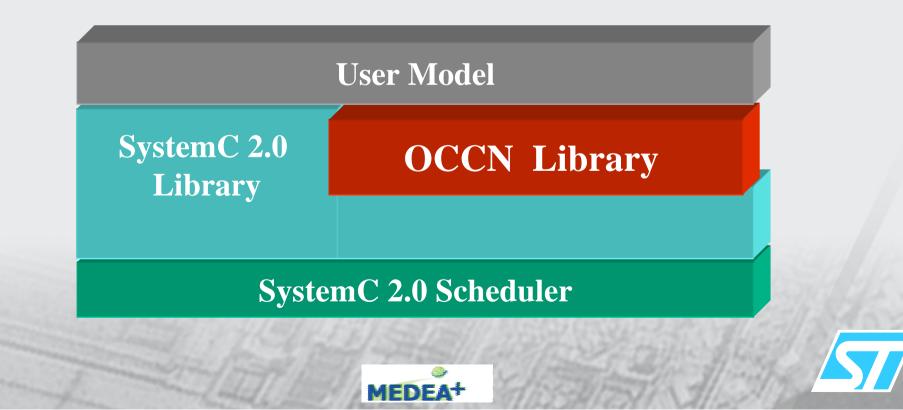

OCCN aims at IC modeling, providing a real **objectoriented methodology** based on a **C++ library** and a fully documented design flow **based on SystemC 2.0**

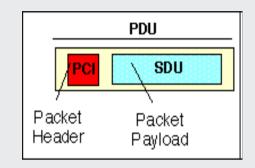

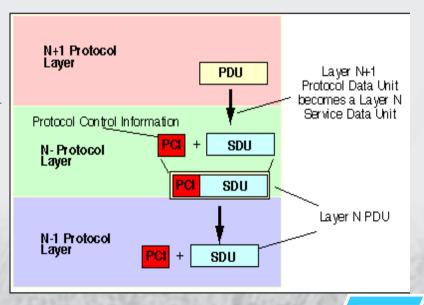

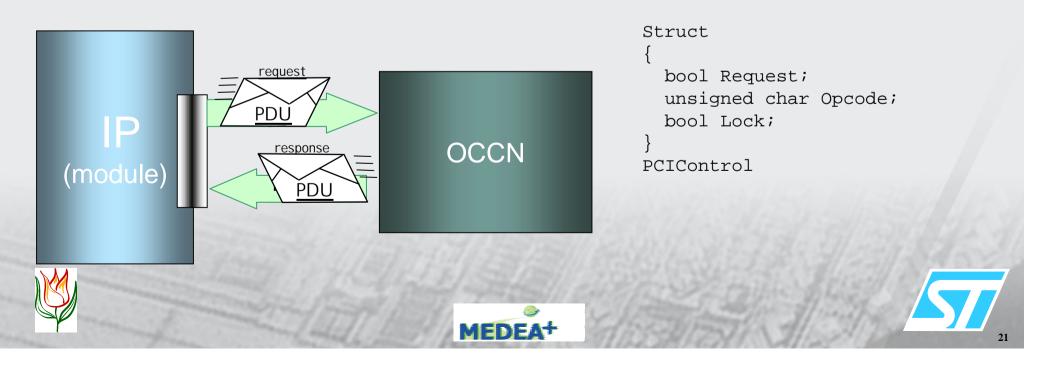

### OCCN core: the PDU

- Protocol = syntax + semantics

- syntax = PDU

- semantics = how the PDU are exchanged

- The PDUs exchanged have two parts:

- a header also known as the Protocol Control Information (PCI)

- a payload also known as a Service Data Unit (SDU)

- Several operators are defined for handling protocol operations

# **PDU Examples** 8 bits Pdu<char> p1; Т Data P

Struct DSLINK\_token {unsigned int P:1; unsigned int T:1};

Pdu<DSLINK\_token,char> p2;

occn\_hdr(pk1,P)=1;

#### Generic representation of a connection

- Any connection of a module to the communication node (network) is based on 2 sets of <u>PDU</u>

- <u>Pdu<uint32,PCIRequest></u>

- <u>Pdu<uint32,PCIResponse></u>

- The PCI sets are described thanks to C/C++ structures. They are defined according to the bus specification and thus are specific to a model. For instance it will be different for an AHB model and an STBUS model

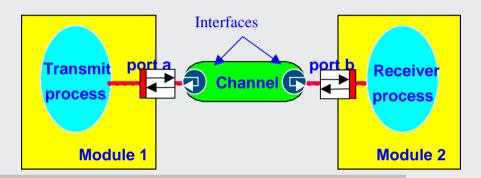

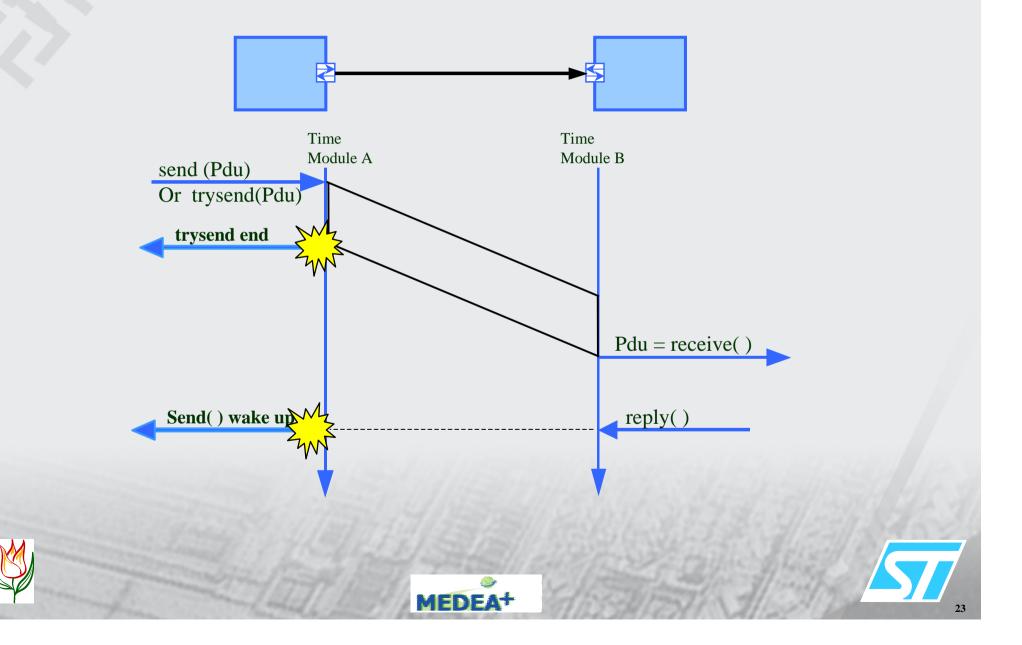

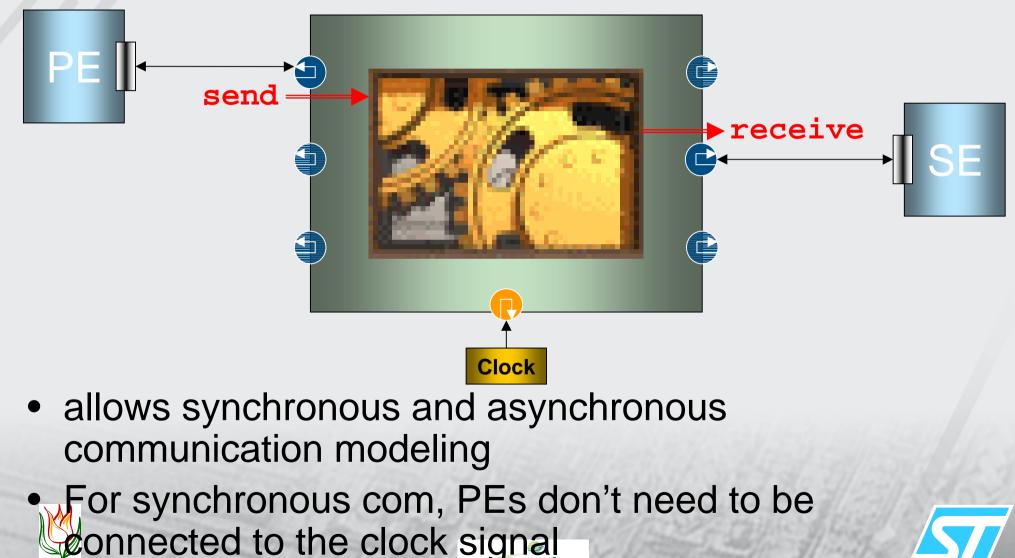

#### **OCCN:** communication

- SystemC based

- Simple Message Passing API

- Pdu<...>\* send(Pdu<...>\* p, sc\_time& time\_out=-1);

- int trysend(Pdu<...>\* p);

- Pdu<...>\* receive(int ack\_time, sc\_time& time\_out=-1);

- Pdu<...>\* receive(sc\_time& ack\_time, sc\_time& time\_out=-1);

- Pdu<...>\* receive(sc\_time& time\_out=-1);

- void reply(Pdu<...>\* p=0);

### OCCN core : API semantic

### OCCN core : protocol state machine centralized

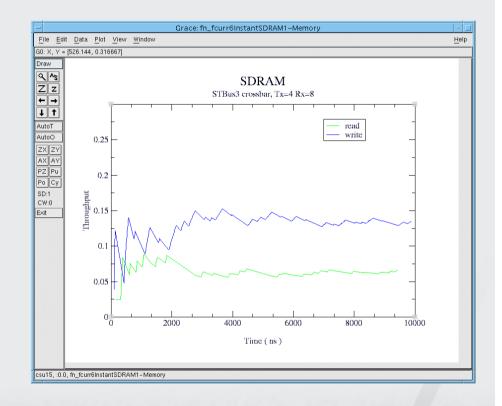

### Performance measurement with Grace

XY graph, XY charts, pie charts, polar, and fixed graphs.

- User-defined scaling, ticks, labels, symbols, line styles, fonts, colors. Merging, validation, cumulative average, curve fitting, regression, filtering, DFT/FFT, cross/autocorrelation, sorting, interpolation, integration, differentiation...

- Internal language, and dynamic module loading (C, Fortran, etc). Hardcopy support with PS, PDF, GIF and PNM formats.

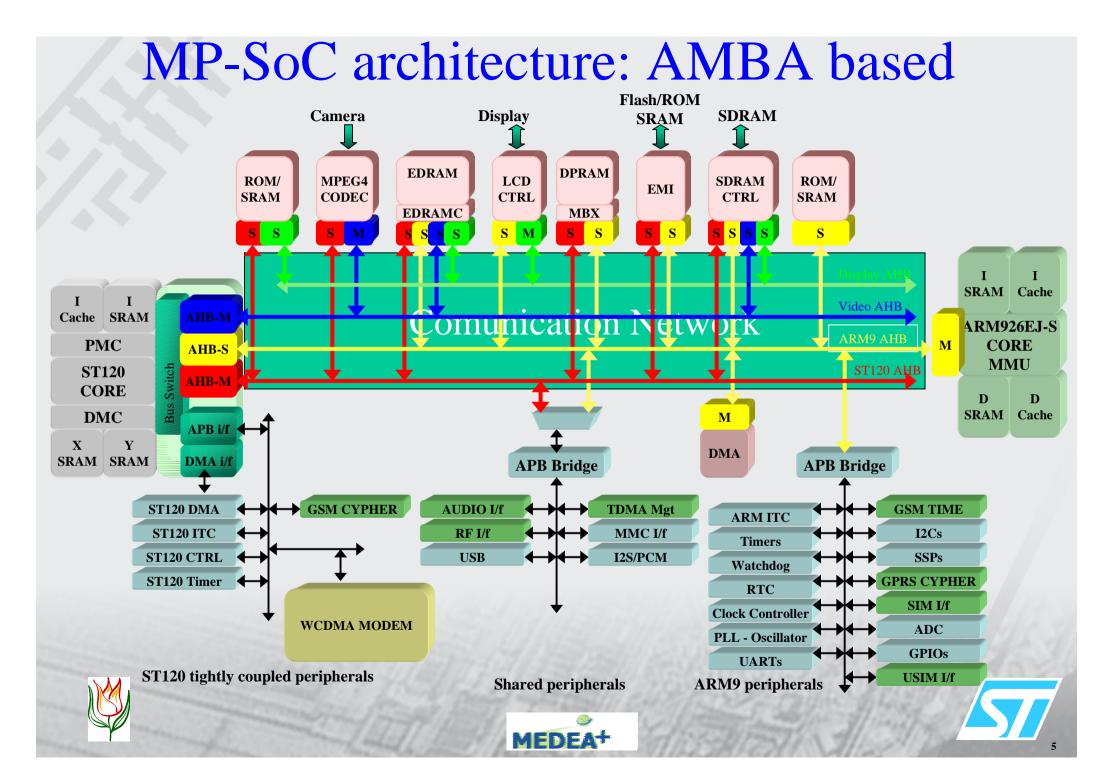

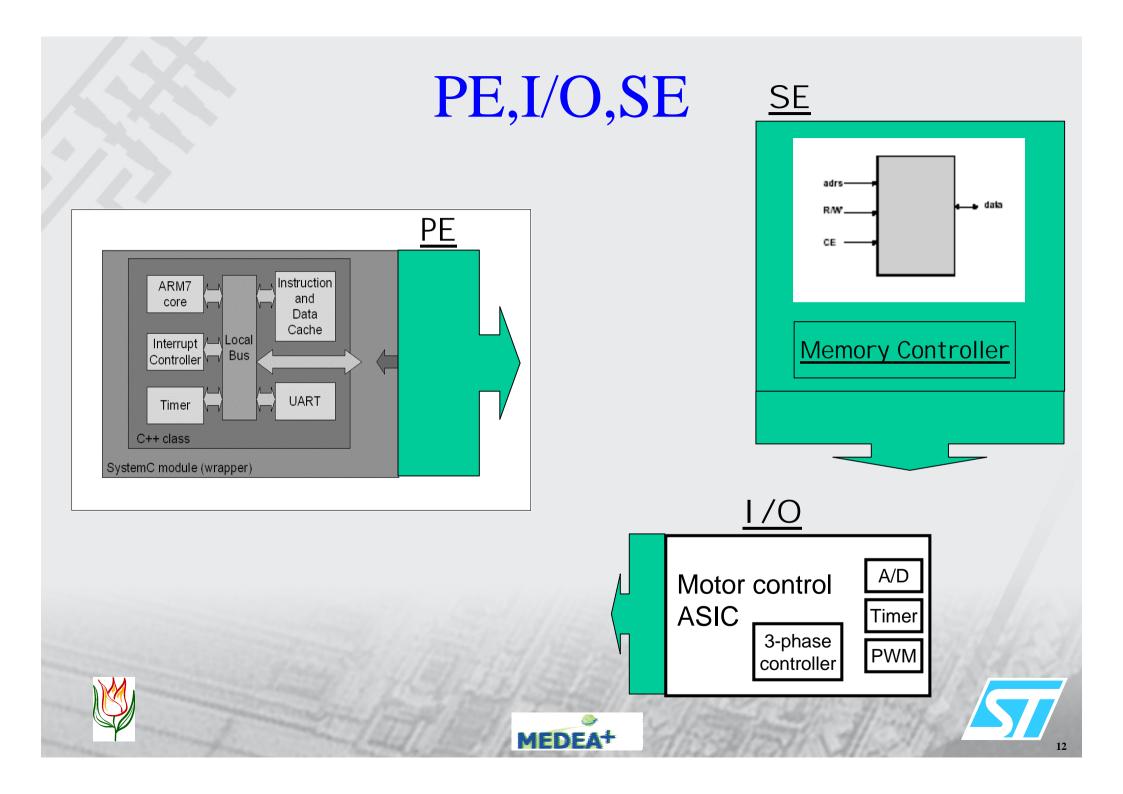

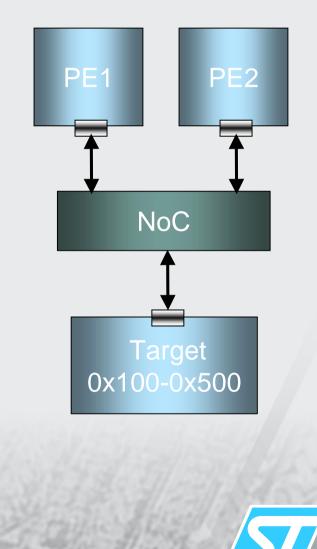

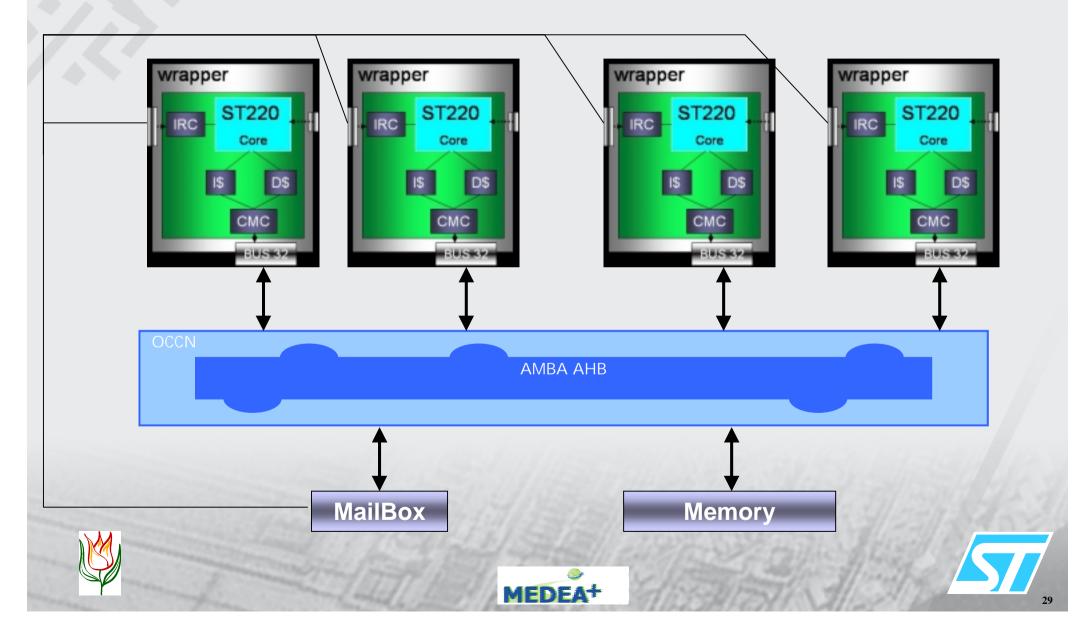

### MP SoC architecure

#### main()

```

sc_clock my_clock(10, SC_NS);

PE pe1, pe2;

SE se;

NoC occa();

```

```

occa.clk(my_clock);

pe1.port(occa);

pe2.port(occa);

se.port(occa);

```

```

occa.set_address_range(&sel.port,0x100,0x500);

occa.set_priority(&pel.port, 2);

occa.set_priority(&pe2.port, 5);

sc_start(-1);

```

#### **OCCN:** PE code example

```

#include "producer.h"

producer::producer(sc_module_name name) : sc_module(name)

{SC_THREAD(read);}

```

} // after the send the msg is not usable

```

void producer::read() {

char c;

Pdu<char>* msg;

while (cin.get(c)) {

msg = new Pdu<char>;

// producer sends c

*msg = c;

out.send(msg);

```

Protocol inlining: protocol is automatic generated

```

MEDEA+

```

## Case Study: NoC Platform

## Some preliminary numbers

- We are able to boot linux

- on a 450Mhz machine

- 7 millions of bundles

- Without cache, bus and memory waiting times, we got

3 minutes

- Without cache and using TLM CA bus, we got 10 minutes

- Expectation on a linux machine 3 minutes

# Conclusion 1/2

- OCCN

- based on SystemC methodology

- open & flexible API

- simulation speed-up

- reusability

- productivity

- communication architecure exploration

- Similar work: Gigascale Silicon Research Center (GSRC) effort Princeton University: MESCAL Project Modern Embedded Systems Compilers Architectures and Languages

Princeton and UC Berkeley

# Conclusion 2/2

- Research Activity funded in Medea

- Public part -> http://occn.sourceforge.net

Univ. of Bologna